ED3-6

Efficient Timing Fault Simulation of Rapid Single-Flux-Quantum Logic Circuits Considering the Pipelined Behavior

Dec.2 10:25- 10:40 (Tokyo Time)

Graduate School of Engineering, Mie University1

School of Engineering, Chuko University2

Graduate School of Informatics, Kyoto University3

We present a fault simulation method for Rapid Single-Flux-Quantum (RSFQ) logic circuits.

Recently, large scale RSFQ logic circuits are designed, fabricated and measured in laboratories. Currently, in test of a fabricated RSFQ chip, ad hoc test patterns are fed to the chip and the outputs are observed. However, by ad hoc method, we cannot deal with large circuits or guarantee to detect faults. Therefore, we need an unambiguous fault model and a test pattern generation for RSFQ circuits.

In RSFQ circuits, a correct arrival order of pulses at input ports of a gate makes the gate work correctly. To model a fault caused by the order which physical factors disturb, we define a timing fault of an RSFQ as the state that the arrival order of pulses at input ports of a gate, including the clock port, is discrepant between the design and the circuit under test. Based on this fault model, we can develop a test pattern generation method. Feeding two consecutive patterns to the circuit is necessary to detect a timing fault. The method generates pairs of patterns and executes fault simulation for the pairs. Test pattern sequence is formed as a chain of pairs.

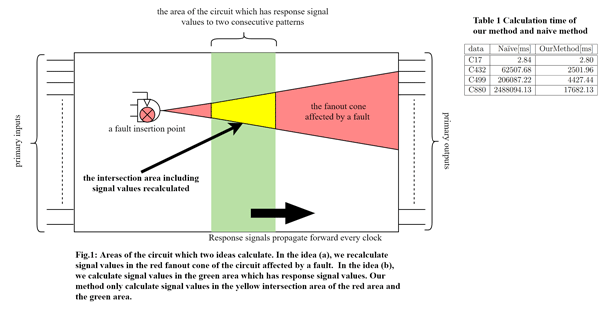

As the test pattern generation repeatedly executes fault simulation, the scalability depends on computational cost of the simulation. In fault simulation in general, a circuit without faults and a circuit with a fault are simulated and their behavior is compared. We propose a computationally efficient fault simulation method based on the two following ideas, as shown in Fig .1. (a)Our method shares calculation for a fault-free circuit and a faulty circuit and recalculates only signal values included in the fanout cone of the fault insertion point. (b)Our method calculates only signal values which are responses to the two consecutive patterns, by utilizing pipelined behavior of RSFQ circuits. Table 1 shows comparison of the calculation time of our method and a naive method for a dataset from ISCAS '85.

Keywords: Circuit Testing, Rapid Single-Flux-Quantum Circuit, Logic Circuit