ED4-6

Investigation and measurement of narrow passive transmission lines for single flux quantum circuits

Dec.2 19:25-19:40 (Tokyo Time)

Graduate School of Engineering Science, Yokohama National University, Japan1

Single flux quantum (SFQ) circuits are known for their low power consumption and high-speed operation [1]. One strong point of SFQ circuits is the availability of passive transmission lines (PTL) for long-distance wiring, where SFQ pulses propagate at nearly the speed of light. Our aim in this study is to reduce the wiring width of PTLs to improve circuit density and to enhance the flexibility in large scale circuit design. The specifical goal is to reduce the PTL width from the 4.8 µm in the present our cell library for the AIST-ADP2 process to 1 µm level.

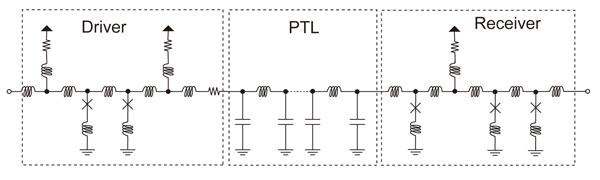

In order to connect an SFQ circuit with a PTL, a driver and receiver are used as an interface. The problem in the connection is the difficulty in the impedance matching between the PTL and the driver/receiver, which is characterized by nonlinear effective impedance. The impedance mismatching causes reflections and resonances and worsens the operating margin. The characteristic impedance of the PTL increases with decrease of the wire width, resulting in the further impedance miss-matching and the deterioration of operating margins.

In this study, the inductance and capacitance of narrow PTLs using the AIST-ADP2 process with the critical current density of 10 kA/cm2 were extracted by Induct EX [3], and the reflection and resonance properties of 1-mm width PTLs with the driver/receiver were investigated by using JSIM to evaluate the bias margins. By optimizing the circuit parameters of the driver and receiver, the bias margins were improved. Similar optimizations were also performed assuming the Josephson process with the critical current density of 25 kA/cm2. We designed ring oscillators using narrow PTLs with the driver and receiver, and measured the delay and the bias margins at high frequency.

Reference

[1] K. K. Likharev and V. K. Semenov, “RSFQ logic/memory family: a new Josephson-junction technology for sub-terahertz-clock-frequency digital systems”, IEEE Trans. Appl. Supercond., 1991.

[2] C. J. Fourie, “Full-gate verification of superconducting integrated circuit layouts with InductEx,” IEEE Trans. Appl. Supercond., 2015.

Keywords: Single Flux Quantum, Passive Transmission Line