ED-1-2-INV

Recent Research on AQFP-Based Accelerator Design

10:30-11:00 28/11/2023

*Olivia Chen1, Naoki Takeuchi2, Renyuan Zhang3, Yanzhi Wang4, Nobuyuki Yoshikawa5

1. Tokyo City University, Japan

2. National Institute of Advanced Industrial Science and Technology, Japan

3. Nara Institute of Advanced Science and Technology, Japan

4. Northeastern University, USA

5. Yokohama National University, Japan

The ever-growing demand for improved power and speed has led researchers to explore emerging technologies that use novel devices and computing paradigms. Josephson-junction-based superconductive electronics (SCE), which have extremely high speed and low power consumption, have been studied for years and are seen as potential candidates for future high-performance computing.

The SCE-based logic families utilize magnetic flux quantization and quantum interference in Josephson-junction (JJ)-based superconductor loops. In SCE, information is stored in superconductor loops as tiny magnetic flux quanta and transferred as several picosecond-wide voltage spikes with quantized area [1, 2]. Fundamentally, the power dissipation in SCE circuits is defined by the energy loss during a switching event in a JJ, which can go below one attojoule. Furthermore, thanks to the lossless transmission feature of superconductor stripe lines, signals can travel at the speed of light between SCE gates. Based on these features, SCE logic families have been perceived as important candidates in the post-Moore era due to their superior potential in operation speed and energy efficiency.

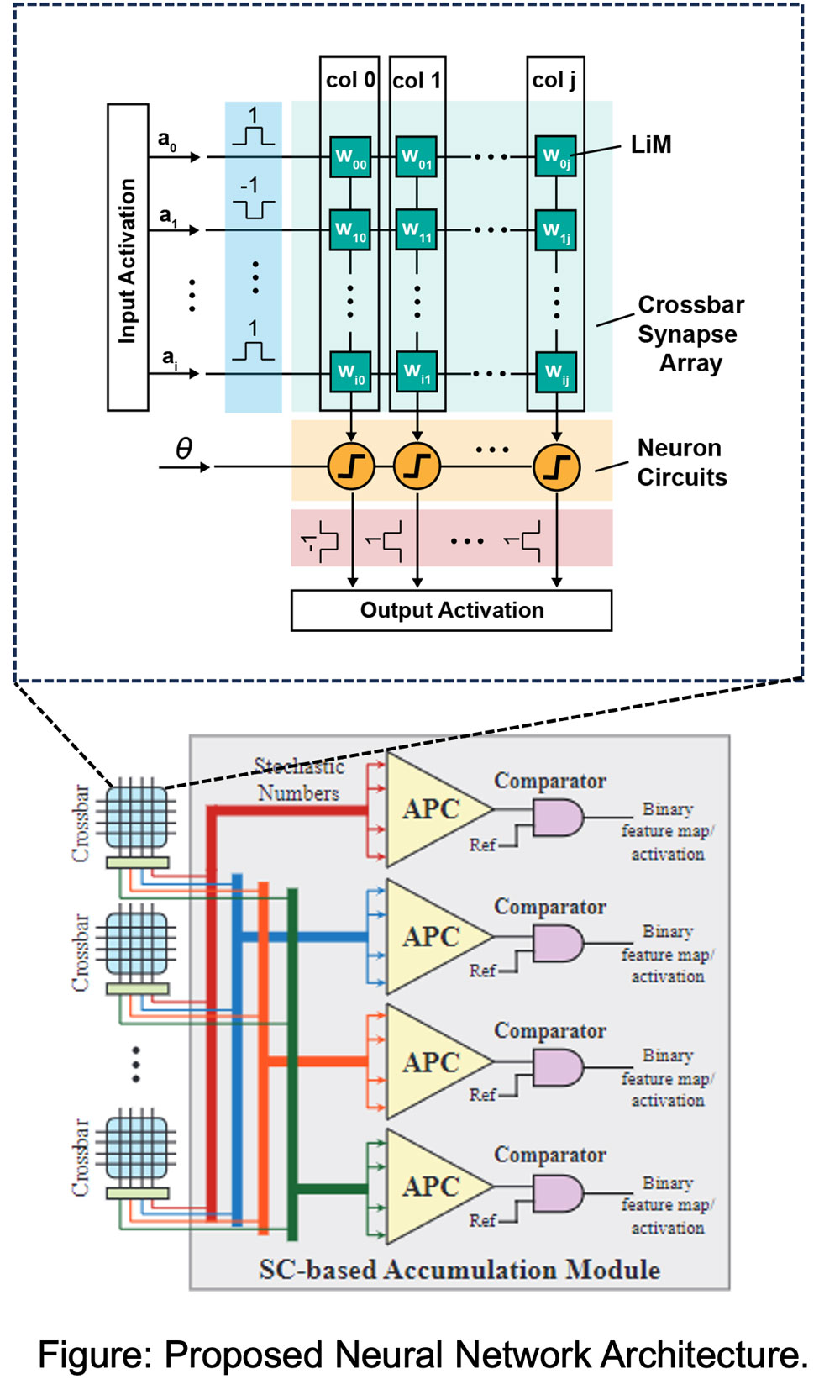

The Adiabatic Quantum-Flux-Parametron (AQFP) is an SCE-based logic family renowned for its exceptional energy efficiency. By using unique current polarities to represent logic '0' and '1', AQFP devices are optimally suited for computations in the binarized computing paradigm, offering extremely high parallelism.

In this paper, we shed some light on our latest progress in crafting high-performance computing systems to boost AI-based computational tasks via a binarized AQFP neural network architecture. We also introduce a software-hardware co-optimization strategy to address the common challenges of algorithm-device mismatches inherent in new device-based designs. Moving forward, we also explore the possibility of a heterogeneous acceleration framework incorporating both CMOS and varied SCE technologies.

・ K. Likharev and V. K. Semenov, “RSFQ logic/memory family: a new Josephson-junction technology for sub-terahertz-clock-frequency digital systems,” IEEE Transactions on Applied Superconductivity, vol. 1, no. 1, pp. 3–28, Mar. 1993.

・ Takeuchi, D. Ozawa, Y. Yamanashi, and N. Yoshikawa, “An adiabatic quantum flux parametron as an ultra-low-power logic device,” Superconductor Science and Technology, vol. 26, no. 3, p. 035010, 2013.

This work was supported by JST FOREST Program (Grant Number JPMJFR226W, Japan) and JSPS KAKENHI Grant Number JP22H0220.