ED3-1-INV

qPALACE: A Suite of EDA Tools for Synthesis and Physical Design Optimization of Single Flux Quantum Logic Circuits

Dec.2 09:00-09:25 (Tokyo Time)

University of Southern California1

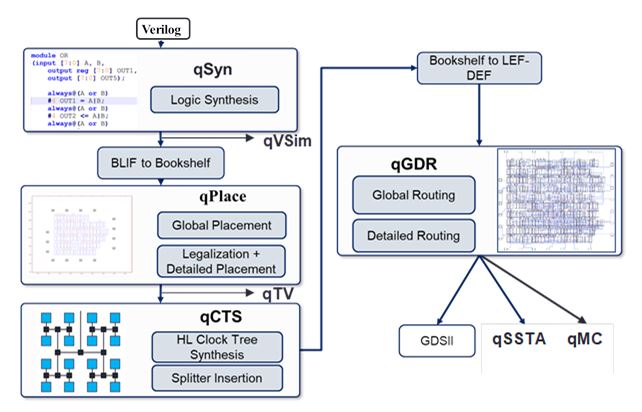

With switching speeds in hundreds of GHz and energy dissipation of 10^−19 Joules per JJ transition, single flux quantum (SFQ) circuits can provide the speed and energy efficiency for beyond-Exascale computing. qPALACE is a suite of modeling, simulation, analysis, and design optimization tools that take a behavioral Verilog description of a target SFQ circuit and generate a GDS-II description of post place&route RSFQ/ERSFQ circuit with proper circuit-level timing, margin, and power characterizations. The flow utilizes many point tools for synthesis (qSyn), physical design (qPlace, qCTS, qGDR), post-routing timing optimization, statistical static timing analysis (qSSTA), margin calculation (qMC), equivalence checking (qEC), logic simulation (qVSim), test pattern generation, timing verification (qTV), ERSFQ biasing, and so on (see Figure.) The qPALACE cell library comprises SFQ-to-DC and DC-to-SFQ conversion cells, clocked Boolean logic cells, D flip-flop, non-destructive readout cell, and passive transmission line driver/receiver cells. Correct functionality and acceptable critical margins (> 20%) of cells have been verified using WRSpice simulation under different process corners. Based on a GDS-II design generated by qPALACE, back-annotated, and simulated, an ERSFQ-based realization of a 32-bit ALU done in the MIT SFQ5ee process node can operate at a clock speed of 30GHz and dissipate less than 2fJ per ALU operation. An implementation of a 32-bit ALU in 14nm GlobalFoundries (GF) FinFET technology with a 0.7V power supply results in a clock frequency of 5GHz and an energy consumption of about 1pJ per ALU operation. A key observation based on the analysis of critical path delay distribution in the ALU circuit is that the most critical timing paths (which set the maximum frequency of the operating clock) are those that connect pads around the chip periphery to the first or last level logic cells or those that go through many non-clocked splitter cells in order to distribute a single source signal to multiple destination cells. Moreover, the overhead of path balancing DFF’s and signal splitters is high, amounting to about 60% of the total JJ count. The research is based upon work supported by the IARPA SuperTools program.

Keywords: Superconductor Electronics, Single Flux Quantum Logic, Electronic Design Automation