ED3-4

Static Timing Analysis of an RSFQ Circuit Considering Timing Jitter

Dec.2 09:55-10:10 (Tokyo Time)

Graduate School of Informatics,Kyoto University,Sakyo-ku, Kyoto 606-8501, Japan1

Graduate School of Engineering,Mie University, Tsu, Mie 514-8507, Japan2

A static timing analysis (STA) method of a Rapid Single-Flux-Quantum (RSFQ) circuit considering timing jitter is proposed. It makes timing design of a circuit more reliable.

We consider STA of a circuit with a single clock source. In STA, for each gate, the arrival times at its inputs (both data inputs and clock input) are calculated, and then, whether they satisfy time constraints, such as setup and hold time constraints, is checked. The time constraints are defined on the difference between a pair of arrival times at gate inputs.

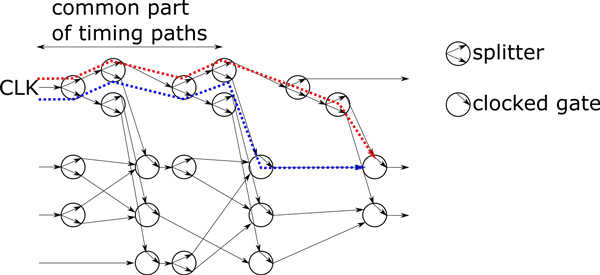

The arrival time at a gate input is calculated as the delay on the timing path from the clock source to it. At a clocked gate, the timing path leads from the clock input to the output, because the timing of the output depends solely on the timing of the clock input. A timing jitter exits in the delay on a timing path, and therefore the arrival time at a gate input also has a timing jitter.

In the proposed method, when calculating the difference between a pair of pulse arrival times at gate inputs with taking into account the timing jitters, we exclude the timing jitter on the common part of the timing paths. This procedure makes the STA result more accurate.

Keywords: RSFQ circuit, timing jitter, static timing analysis