ED7-4-INV

3D integration of superconducting quantum systems

*Cyrus F. Hirjibehedin1

- Lincoln Laboratory, Massachusetts Institute of Technology1

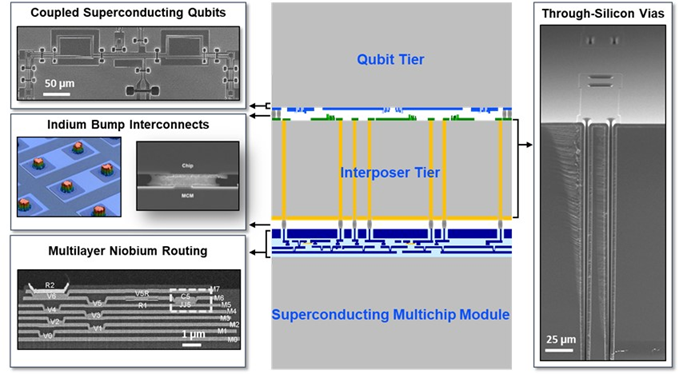

As quantum systems progress towards the scale needed for a broad range of quantum computing applications, quantum scientists and engineers are addressing the challenge of developing robust systems-level readout and control of multi-qubit systems. We describe a 3D-integrated 3-tier stack architecture for superconducting quantum circuits (Fig. 1) to enable enhanced connectivity while preserving qubit coherence. The top qubit tier is fabricated using dielectric-free (single-layer) processing that supports high qubit coherence. At the bottom is the superconducting multichip module (SMCM) tier, which has multiple superconducting metal layers coupled via interconnects through oxide layers for advanced DC and RF signal routing. Connecting the outer two tiers is an intermediate active interposer tier that is connected to the other two tiers by indium bumps. The interposer provides access to multi-level superconducting circuitry by utilizing superconducting through-silicon vias (TSVs) while preserving qubit performance by isolating the qubits from lossy dielectrics in the SMCM routing tier. Our active interposer also provides additional levels for resonators and qubits to be integrated into the system and enables novel circuit elements that incorporate TSVs.

Robust, high-yield connectivity between the three tiers is confirmed using metal chains with thousands of links that traverse the three tiers. Furthermore, we demonstrate the operation and local control of high-coherence capacitively-shunted flux qubits (CSFQs) in a 3D-integrated 3-tier architecture. Qubits are fabricated both on the qubit and interposer tiers using high-coherence processes. Readout and control components, including resonators and flux bias lines, are located on the interposer tier, and are accessed using TSVs and bump bonds from a bottom-tier SMCM. Coherence of the CSFQs in the 3D-integrated stack is consistent with values typical for the single-tier processes – including with the dielectric-containing multilayer SMCM tier electrically coupled through the three-tier stack.

This research was funded in part by the Office of the Director of National Intelligence (ODNI), Intelligence Advanced Research Projects Activity (IARPA) and the Defense Advanced Research Projects Agency (DARPA) under Air Force Contract No. FA8702-15-D-0001. The views and conclusions contained herein are those of the authors and should not be interpreted as necessarily representing the official policies or endorsements, either expressed or implied, of the ODNI, IARPA, DARPA, or the U.S. Government.

Figure 1 – 3D integrated 3-tier stack architecture. The 3-tier stack allows the superconducting multichip module (SMCM), which enables multilayer signal routing, to be connected to the high-coherence qubit tier through an active interposer tier that has through-silicon vias (TSVs). The individual tiers are connected by indium bump interconnects.