ED7-4

Evaluation of True Random Number Sequences Generated by Utilizing Timing Jitters in Superconducting Integrated Circuits

Dec. 1 12:15-12:30

*Kenta Sato1, Naonori Sega1, Hiroshi Shimada1, Yoshinao Mizugaki1

The University of Electro-Communications, Japan1

SFQ circuitry is attractive to next-generation integrated circuits because it realizes high-speed operation and low power consumption. A Hardware Random Number Generator (HRNG) is one of the applications in SFQ circuitry. Random number sequences are used in various fields such as simulations of natural phenomena and cryptographical communication. Especially, an HRNG, which generates true random number sequences having complete randomness, is required in fields related to information security. True random number sequences are generated by using physical phenomena such as noise, collapse, and chaotic dynamics. In SFQ circuitry, thermal noises in Josephson junctions and shunt resistors induce non-negligible jitters for circuits' operation. Onomi et al. studied SFQ HRNGs that generated true random number sequences utilizing timing jitters by thermal noise, and they operated an HRNG in which the trigger signal had timing jitters longer than the period of a high-frequency Josephson oscillator.

In this research, we proposed an HRNG with two oscillators to enhance stability against variation of oscillator frequencies. We investigated the characteristics of random numbers generated by the proposed HRNG not only by numerical simulation but also by experiments using test circuits fabricated a Nb/AlOx/Nb integration process.

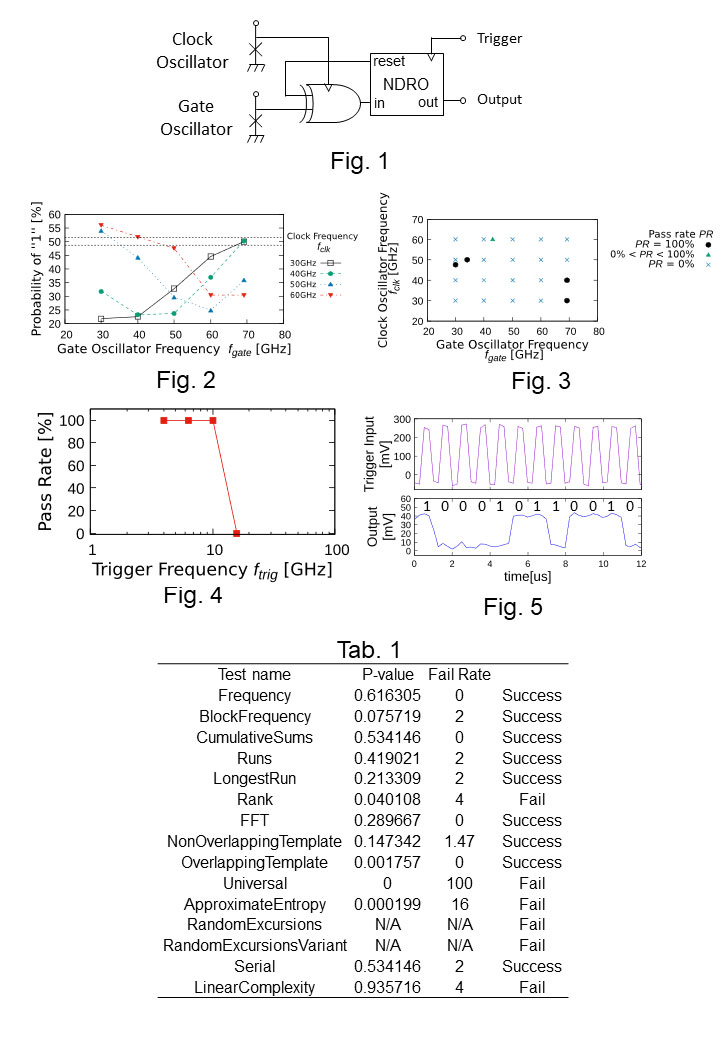

Figure 1 shows a simplified block diagram of the HRNG we designed. We use two oscillators, a Clock Oscillator, and a Gate Oscillator. The oscillators are oscillated by the over-biasing method: a DC voltage is applied to the Josephson junction. The signal from the Clock Oscillator is transferred to the reset terminal of a Non-Destructive Read-Out memory (NDRO), and the clock and input terminals of an XOR gate. Then the signal from the Gate Oscillator is fed to another input terminal of the XOR gate. Signals of two oscillators are fed to the XOR gate with timing jitters, and therefore, the output of the XOR gate becomes truly random. The generated random number is stored in the NDRO, and the random number is obtained from the Output by feeding a Trigger signal at arbitrary time.

The numerical simulation soft we used was JoSIM. Figure 2 shows the Gate Oscillator frequency fgate dependence of the probability of "1" for four Clock Oscillator frequencies fclk at Trigger frequency ftrig of 6.31 GHz. The black dashed lines indicate edges for passing Monobit test in the random number test FIPS 140-2. It shows that the probability of "1" is the local minimum at fclk≅fgate. Figure 3 shows the fclk and fgate dependence of three categories of the pass rate of the FIPS 140-2 at ftrig = 6.31 GHz. The oscillators' frequency conditions for 100% pass rate agree with the conditions for the probability of "1" being in 48.625%-51.375%. Figure 4 shows the ftrig dependence of the pass rate of FIPS 140-2 at fclk = 40 GHz and fgate = 69.2 GHz. It operated up to ftrig = 10 GHz.

We designed the HRNG using the Nb 10kA/cm2 process. Figure 5 shows the voltage wave-form converted from SFQ signals generated by the HRNG. Table 1 shows the result of the random number test SP800-22, which is a stricter test than FIPS140-2, for 50 samples of 20 kbits random number sequences generated at ftrig = 1 MHz, fclk = 48.79 GHz, and fgate = 19.81 GHz. It shows the results of 9 in 15 tests were "Success". On the other hand, "Rank", "RandomExcursions", "RandomExcursionsVariant", and "LinearComplexity" tests were "Fail" because the length of random number sequences was too short, while "Universal" test was known to be unsuitable.

Keywords: Superconducting integrated circuit, SFQ circuit, Hardware random number generator, True random number